|

|

| |

Global Partners

Exclusive Representative Contract

with Global Companies |

|

|

|

IP Core 제품 > Cable > Multi-channel DVB-C J83 modulator |

| |

|

Multi-channel DVB-C/J83 modulator |

| Product code: CMS0024 |

|

The CMS0024 multi-channel DVB-C/J83 modulator is fully compliant with the

European, US and Japanese downlink cable Standards DVB-C EN 300 429 and ITU J83

Annexes A/B/C (including DOCSIS 1.1/2.0). The core provides all the necessary

functions between transport stream input and a modulated QAM output.

The core

can be configured to support from one to four FDM channels with additional

(independent) channels accommodated by the instantiation of multiple single or

multi-channel cores per FPGA.

Multi-channel J.83B designs can operate either

from internal memory (short interleaving modes) or from shared external memory

(long interleaving modes) by means of a versatile access controller.

Typical

applications of the CMS0024 include head-end video and broadband data

transmissions systems (CMTS), cable modem test equipment and point-to-point

(PTP) or point-to-multipoint microwave radio links.

A range of synthesis

options allows the core to be tailored for any particular application.

Also

see: |

|

DVB-C/J83 modulator

DVB-C/J83 demodulator

Universal

QAM/PSK modulator

|

|

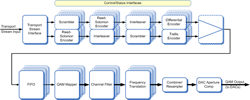

Block diagram

Click on image for further information

|

|

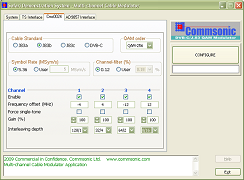

Safari Plug-in

Click on image for further

information

|

|

Downloads

E-mail

me when these downloads are updated |

|

Certification

| |

|

Standards compliance

DVB-C EN 300 429

ITU J83 Annexes A/B/C

DOCSIS 1.1/2.0 |

|

Features

Modulation accuracy > 45dB (MER).

Variable symbol rate interpolation.

Software selectable channel filter.

On-chip or off-chip interleaver memory.

1 to 4 channels per core.

Single or multiple standards per core.

Multiple cores provide > 4 channels. |

|

Applications

Head-end digital video and broadband data (CMTS) transmission systems.

Next generation, bandwidth-on-demand CMTS systems employing channel-

bonding. |

|

Implementation

Optimised for Altera.

Evaluation boards available. |

|

Plug-ins / Extensions

ASI/SPI

interface with TS PCR rate

adaptation. | | |

| | |